Sterownik monochromatora na bazie układu FPGA

Wiele badań eksperymentalnych wymaga wykonania serii pomiarów z jednoczesnym przemieszczaniem elementów układu pomiarowego. Takie pomiary muszą być wykonane szybko, aby parametry badanego układu nie zmieniały się w trakcie ich realizacji. W związku z tym proces ten wymaga automatyzacji.

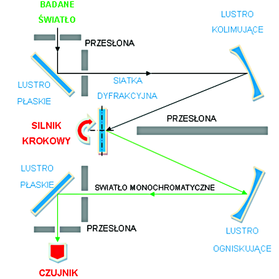

Do tej kategorii urządzeń należy monochromator – przyrząd przeznaczony do analizy spektralnej światła. Zasada jego działania polega na rozszczepieniu wiązki światła, na przykład za pomocą siatki dyfrakcyjnej, i wykonaniu selektywnych pomiarów składowych widma. Pomiary takie wykonywane są nieruchomym czujnikiem, a wybór długości fali realizuje się poprzez obrót siatki dyfrakcyjnej. Schematycznie budowę monochromatora pokazano na rys. 1. Kolorem czerwonym zaznaczono elementy wykonawcze współpracujące ze sterownikiem [5].

Sterowniki tego typu urządzeń realizowane są zazwyczaj na bazie mikroprocesorów. W ramach działalności SKN Spektrum podjęto próbę zaprojektowania sterownika wyspecjalizowanego do tego celu, bazującego na układzie programowalnym FPGA. W trakcie realizacji tej pracy wykorzystano elementy wcześniej opracowanej w ramach działalności koła biblioteki VHDL [1].

Do realizacji projektu zastosowano język VHDL [3, 4]. Umożliwia on wykonanie opisu struktury lub funkcji urządzenia, jego dekompozycję na mniejsze bloki oraz syntezę układu [2]. Projekt zrealizowano w pakiecie narzędziowym ISE firmy Xilinx w wersji 10.1 [6], a do symulacji wykorzystano program ModelSim XE III 6.3g [6]. Jest to darmowe, w pełni funkcjonalne oprogramowanie, wystarczające do realizacji nawet bardzo złożonych projektów.

Projekt zaimplementowano w układzie FPGA Spartan 3E [6], zainstalowanym w zestawie prototypowym Basys firmy Digilent oraz przetwornik pomiarowy PmodAD1 – Two 12-bit A/D tej samej firmy [4].

Funkcje realizowane przez sterownik

Zadaniem sterownika jest wykonanie serii pomiarów z jednoczesnym pozycjonowaniem siatki dyfrakcyjnej, zapisem wyników i ich prezentacją graficzną. Do inicjalizacji i odczytu stanu przetworników pomiarowych w układzie zaimplementowano interfejs szeregowy SPI. Podstawowe parametry pracy układu zadawane są z typowej klawiatury komputerowej, co wymagało implementacji interfejsu PS/2. Siatka dyfrakcyjna pozycjonowana jest za pomocą silnika krokowego. Sterownik tego silnika stanowi kolejny element zaimplementowany w strukturze. Ostatnim elementem projektu jest interfejs VGA zaimplementowany w celu podłączenia monitora i wizualizacji wyników.

Realizacja projektu

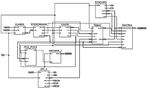

Schemat sterownika opracowanego w pakiecie ISE WebPack pokazano na rys. 2. Składa się on z opracowanych w ramach projektu dziewięciu bloków, które realizują wcześniej przedstawione funkcje sterownika.

Za komunikację sterownika z klawiaturą komputerową, podłączoną do portu PS/2 zestawu uruchomieniowego, odpowiadają dwa moduły: KLAWIA oraz STEROWANIE. Moduł KLAWIA służy do odczytu numeru kodu wciśniętego klawisza. Jednorazowe naciśnięcie klawisza, niezależnie od czasu jego przytrzymania, generuje jedną ośmiobitową wartość, która przesyłana jest do modułu STEROWANIE. Moduł STEROWANIE dokonuje konwersji numeru klawisza na sygnały sterujące, takie jak reset, start/stop lub zmiana po skoku wielkości mierzonej.

Za synchronizację odczytu stanu przetwornika analogowo-cyfrowego, zapisu wyników oraz obrót siatki dyfrakcyjnej odpowiada moduł LICZNIK. Moduł ten przetwarza sygnał zegarowy o częstotliwości 50 MHz, taktujący pracę modułu prototypowego, na sygnały sterujące pracą tych modułów. Zmierzone wartości zapamiętywane są w module REJESTR. Za pozycjonowanie silnika krokowego odpowiada moduł POZ_POCZ.

W projekcie nie wykorzystano dostępnej w układzie Spartan pamięci. Do przechowywania wyników pomiarów w module REJESTR utworzono tablicę 10-bitowych wartości typu std_logic_vector. Do każdego elementu tej tablicy zapisywany jest ośmiobitowy wynik pomiaru (osiem młodszych bitów) oraz kod skoku między pomiarami (dwa starsze bity). Tablica posiada dwa niezależne porty: do zapisu i odczytu. Zapis danych synchronizowany jest z pracą modułu POZ_POCZ, a odczyt z licznikiem synchronizacji poziomej, co umożliwia jednoczesne wyświetlanie całej zawartości tablicy. Moduł POZ_POCZ kontroluje pozycję silnika, zliczając liczbę kroków wykonanych przez silnik w czasie wykonywania serii pomiarów i realizuje powrót układu do pozycji początkowej po zakończeniu pomiarów. Moduł ten umożliwia zadawanie liczby kroków silnika pomiędzy kolejnymi pomiarami.

Wyświetlanie wyników pomiarów na monitorze w postaci wykresu punktowego realizują moduły SYNCHRO oraz GENOBRA. W pierwszym z nich wykorzystano fragmenty kodu zaczerpnięte z programu demonstracyjnego dołączonego do zestawu uruchomieniowego, dostosowując ten kod do potrzeb tego projektu. Jedną z ważniejszych zmian wprowadzonych w tym module jest dwukrotne zwiększenie częstotliwości jego pracy. Drugi moduł, GENOBRA, odpowiedzialny jest za prezentację zawartości tablicy wyników w module REJESTR oraz opcji menu sterownika w postaci wykresu na ekranie monitora. Praca tego modułu oparta jest o stany liczników synchronizacji pionowej i poziomej modułu SYNCHRO.

Moduł transmisji danych SPI_II odpowiada za komunikację pomiędzy układem a przetwornikiem analogowo-cyfrowym. Transmisja odbywa się magistralą szeregową SPI. Ze względu na rozdzielczość monitora, z dwunastu bitów przesłanych do układu z przetwornika, tylko osiem najstarszych przesyłanych jest do modułu REJESTR. Dane odczytywane z przetwornika są jednocześnie wysyłane do portu wyjściowego układu, co umożliwia ich archiwizację w pełnej rozdzielczości w pamięci zewnętrznej.

Ostatni z modułów, STEROWNIK_X, przekształca jednobitowy sygnał taktujący pracę silnika krokowego oraz jednobitowy sygnał ustalający kierunek na czterobitowy sygnał sterujący pracą silnika krokowego, zgodnie z zadanym algorytmem.

Po wykonaniu syntezy układu sterownik umożliwia wykonywanie pomiarów, przesyłanie wyników magistralą szeregową do bloku rejestrów, wizualizację wyników w postaci wykresu punktowego na monitorze VGA oraz wysłanie wyników magistralą szeregową SPI do urządzeń zewnętrznych.

Możliwości sterownika

Sterownik ten opracowano do celów demonstracyjnych, w związku z czym ograniczono jego funkcjonalność do podstawowych funkcji. Układ umożliwia wstrzymanie i wznawianie pomiarów w dowolnej chwili. Po wykonaniu serii pomiarów silnik krokowy powraca do pozycji początkowej. Użytkownik ma możliwość wyboru, co ile skoków silnika wykonane zostaną kolejne pomiary (jeden, dwa, cztery lub osiem). Wartość ta zmieniana może być w dowolnej chwili, również w trakcie wykonywania serii pomiarów i zostaje natychmiast uwidoczniona na wykresie w postaci zmiany koloru wyświetlanych na monitorze punktów. Dla ułatwienia odczytu wykresu dodana została opcja siatka, która umożliwia wyświetlenie na wykresie podziałki. Układ testowy pokazano na rys. 3. Na monitorze po prawej stronie widoczny jest projekt sterownika, a po lewej przykładowe wyniki pomiarów w formie wykresu.

Podsumowanie

Programowalne układy logiczne znajdują coraz szersze zastosowanie. Z powodzeniem sprawdzają się w cyfrowej obróbce sygnałów, w zastosowaniach militarnych, telekomunikacji itp. [2]. Mogą być też wykorzystywane do realizacji wyspecjalizowanych układów sterowania, tak jak w tej pracy, zastępując mikroprocesory. Największą zaletą układów tego typu jest możliwość dowolnego konfigurowania struktury i dokonywania zmian w gotowym projekcie. Równie często układy programowalne wykorzystywane są przez producentów układów scalonych do projektowania i weryfikacji poprawności działania nowych projektów [3, 4].

Przedstawiony w pracy sterownik monochromatora, realizujący szereg czynności związanych ze sterowaniem pracą monochromatora, wykorzystuje 99 % zasobów logicznych układu XC3S100E, który jest najmniejszym układem z rodziny Spartan 3E. Należy zauważyć, że wykorzystanie do realizacji sterownika prawie całych zasobów tego układu nie oznacza osiągnięcia granic jego możliwości. W przypadku modyfikacji układu znaczna część zasobów może zostać zwolniona, jeżeli do zapisu wyników pomiarów zostaną wykorzystane wewnętrzne bloki pamięci RAM [6]. Taka przebudowa struktury sterownika pozwala zwolnić znaczną część zasobów logicznych układu i umożliwia dalszą rozbudowę sterownika o kolejne funkcjonalności, np. dodanie interfejsu szeregowego do transmisji danych do komputera, uśrednianie wyników pomiarów, zwiększenie liczby pomiarów w serii, wprowadzenie opóźnień inicjowania pomiarów po wykonania skoku silnika w celu ograniczenia wpływ drgań układu na wyniki pomiarów, itp. Dalsza rozbudowa układu jest przedmiotem aktualnie prowadzonych prac.

Bibliografia

- Brabański R., Jakubczyk M., Grzesik S., Tomczewski K.: Implementacja elementów biblioteki dla sterownika programowalnego w układach FPGA i CPLD. Materiały z Konferencji Zastosowania Komputerów w Elektrotechnice ZKwE 2008, Poznań, 2008, s. 377 – 378.

- Kalisz J. (red.): Język VHDL w praktyce. WKŁ, Warszawa 2002.

- Majewski J., Zbysiński P.: Układy FPGA w praktyce. BTC, Warszawa 2007.

- Digilent Inc. - Digital Design Engineer's Source

- Verity Instruments - Products

- FPGA and CPLD Solutions from Xilinx, Inc.

inż. Robert Brabański, dr inż. Krzysztof Tomczewski – SKN Spektrum Politechnika Opolska